Overview of the SPI bus

Introduction

SPI(Serial Peripheral interface). It was first defined by Motorola on its MC68HCXX family of processors. The SPI interface is mainly used between EEPROM, FLASH, real-time clock, AD converter, and digital signal processor. SPI is a high-speed, full-duplex, synchronous communication bus, and only occupies four wires on the pin of the chip, saving the pin of the chip and space for the layout of PCB.It is because of this simple and easy to use characteristics, now more and more chips integrate this communication protocol, such as STM32 single-chip processor series.

Characteristic

PIN

- MISO/SDO:Master input slave output

- MOSI/SDI:Master output slave input

- SCLK/SCK :Serial Clock

- SS/CS/CE:Slave Select

Clock Polarity(CPOL)

Clock polarity and phase together determine how data is read, Such as the rising edge of the signal or the falling edge of the signal to read data.

CPOL can be set to 1 or 0. This means that you can set the clock's default state (IDLE) to high or low as needed. Polarity reversal can be achieved with a simple logic inverter. You must refer to the data manual of the device to set CPOL and CPHA.

- CPOL = 0:IDLE:0

- CPOL = 1:IDLE:1

Clock Phase(CPHA)

CPHA: The data is collected at the specific phase or edge of the clock signal

- CPHA = 0:Sampling at the first hop edge of the clock signal

- CPHA = 1:Sampling at the Second hop edge of the clock signal

SPI Mode

| SPI Mode | CPOL | CPHA |

| 0[00] | 0 | 0 |

| 1[01] | 0 | 1 |

| 2[10] | 1 | 0 |

| 3[11] | 1 | 1 |

Advantage

- Full duplex serial communication

- High data transfer rate

- Simple software configuration

- Extremely flexible data transfer, not limited to 8 bits, it can be any size word

- Very simple hardware structure. The slave station does not require a unique address (unlike I2C). Slave machines use a host clock and do not require a precision clock oscillator/crystal oscillator (unlike UART). No transceiver is required (unlike CAN).

Disadvantage

- There is no hardware slave answer signal (the host may have nowhere to send it without knowing it)

- Usually only one master device is supported

- More pins required

- No hardware-level error checking protocol is defined

- Compared to RS-232 and CAN buses, it can only support very short distances

Principle

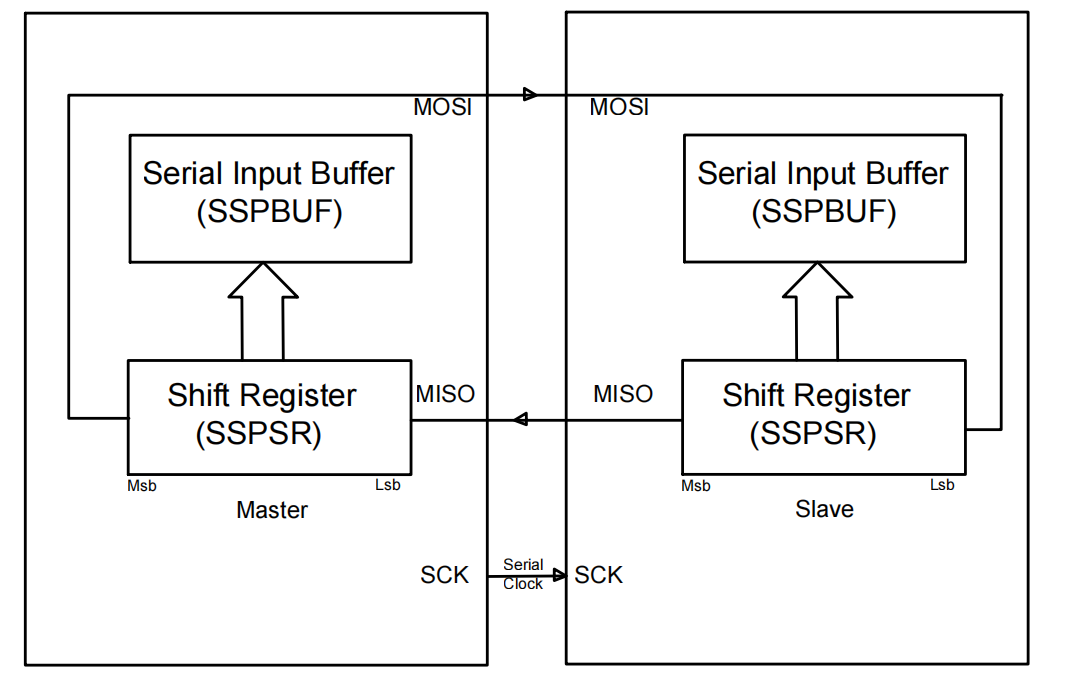

The reason why data transmission between SPI devices is also called data exchange is that the SPI protocol stipulates that an SPI device cannot merely act as a Transmitter or a Receiver in the process of data communication. During each Clock cycle, the SPI device sends and receives a bit of data (regardless of the master or slave device ), which is equivalent to a bit of data being exchanged on the device. If a Slave device wants to receive the control signal from the Master, it must be able to be accessed by the Master device before this. Therefore, the Master device must first select the Slave device through the SS/CS pin to select the Slave device that it wants to access.

During data transmission, each received data must be sampled before the next data transmission. If the received data is not read, the received data may be discarded, resulting in the failure of the SPI physical module. Therefore, programs generally read Data in SPI devices after SPI transfers data, even though these data (Dummy Data) is useless in our program (although the read immediately after sending is meaningless, it still needs to be read from the register).